湖南大学,今日Nature!

2024-05-26

2024-05-26

6762

6762

继2024年2月28日,湖南大学发新年第一篇Nature之后,湖南大学今日再发Nature!有趣的是,这两篇Nature都是来自湖大的物理与微电子科学学院!

二维(2D)半导体,由于其无悬键表面和能够集成到各种衬底上而没有传统的晶格匹配约束,因此在单片三维(M3D)集成方面显示出巨大的潜力。

然而,由于其原子薄的体厚,2D半导体不兼容微电子领域的各种高能工艺,其中多个2D电路层的M3D集成具有挑战性。

在此,来自湖南大学的刘渊等研究者报告了一种替代的低温M3D集成方法,即对整个预制电路层进行范德瓦尔斯(vdW)层压,其中加工温度控制在120℃。相关论文以题为“Monolithic three-dimensional tier-by-tier integration via van der Waals lamination”于2024年05月22日发表在Nature上。

单片三维(M3D)集成技术,最近引起了相当大的兴趣,该技术通过上层的沉积在同一晶圆上依次制造多个堆叠层。这样的3D架构不仅克服了更高设备密度的缩放限制,而且还实现了新的3D计算系统,其中多功能层(如逻辑,存储器和传感器)可以紧密地搭配并垂直互连。

迄今为止,硅基M3D集成的一个主要挑战是其低热预算,其中上层的工艺温度不应超过后端温度,通常低于450°C,以避免性能下降和掺杂物扩散到下层。由于硅晶体管需要在更高的温度下制造,通常大于600°C,因此热预算限制了M3D集成系统的发展。因此,迫切需要探索新的半导体和集成工艺,以实现未来的M3D集成。

最近,二维(2D)半导体在M3D集成方面显示出了巨大的潜力。利用无悬垂键的表面,可以在相对较高的温度下预合成二维半导体,然后在低于200℃的低加工温度下进行物理转移。这种方法可以克服热预算的主要限制,保证下层器件的质量。

此外,2D半导体具有原子级薄的体厚,可以大大减少短通道效应、失态泄漏电流和相关的热量产生,这些也是多个器件垂直堆叠在一起时3D集成的关键问题。

然而,使用2D半导体组装多层M3D系统是一个巨大的挑战,因为在M3D集成中,每个电路层不仅包括半导体层,还包括其他有源和无源层,如触点、栅极介电体、互连、层间介电体(ITD)和连接相邻层的层间通孔(ITVs)。

在现代微电子学中,这些功能层的集成通常基于高能或高温沉积工艺,这通常与具有原子厚度的精细二维晶格不兼容。例如,高κ栅极介电层和低κ过渡层通常分别使用原子层沉积和等离子体增强化学气相沉积沉积,这很难应用于无悬键的二维表面。

同样,过渡段、独立段和金属触点的产生分别涉及高能等离子体、反应性离子蚀刻和金属蒸气,这些也被证明会降解或破坏单层晶格。一旦多个电路层随后被制造和堆叠,这些限制可能会成倍放大,极大地影响底层器件的性能和集成成品率。

因此,迫切需要开发一种低能量的M3D工艺,既能保留固有的2D特性,又能集成多个2D电路层。

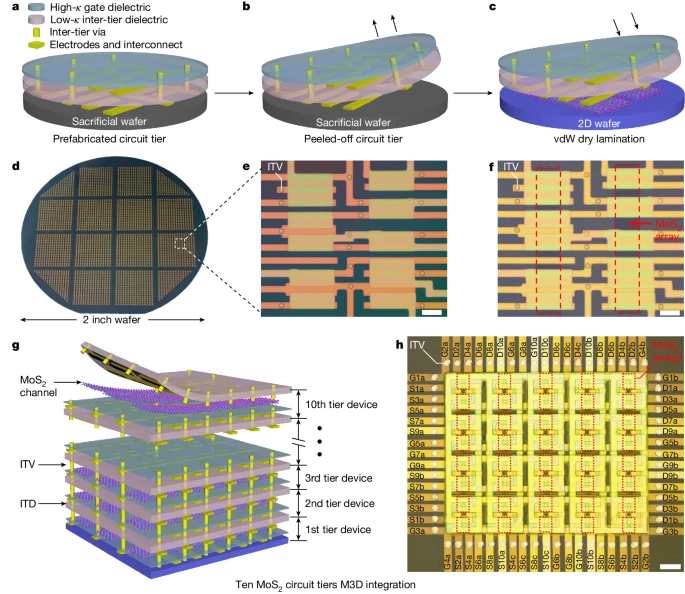

在此,研究者报告了一种基于一步范德华(vdW)集成方法的低温M3D集成方法。在该技术中,所有必要的器件和电路元件都预制在牺牲晶圆上,包括低-κ ITD、源极、漏极和栅极、高-κ栅极电介质、平面内互连和垂直ITVs。随后,所有器件组件作为一个整体电路层从牺牲晶圆中机械释放出来,并在120°C的加工温度下物理层压在2D半导体的顶部,从而避免了直接在2D晶格上的各种侵蚀性工艺。

在此基础上,研究者实现了一个具有10层电路的M3D系统的大规模vdw集成。详细的电气特性表明,在顶部集成多个电路层后,底部的2D晶体管不会受到影响,这与导致性能下降的传统制造工艺相反。

此外,通过垂直互连位于不同层内的设备,实现了各种协作设备功能,包括逻辑对存储器和传感器对逻辑。研究者的研究展示了一种可替代的低能量方法,通过层层vdW层压来制造晶圆级和多层M3D系统,

这可能为具有更多层数的二维半导体的M3D集成或与传统微电子工艺不兼容的其他新兴半导体的3D集成提供令人兴奋的影响。

图1 逐层的M3D集成流程。

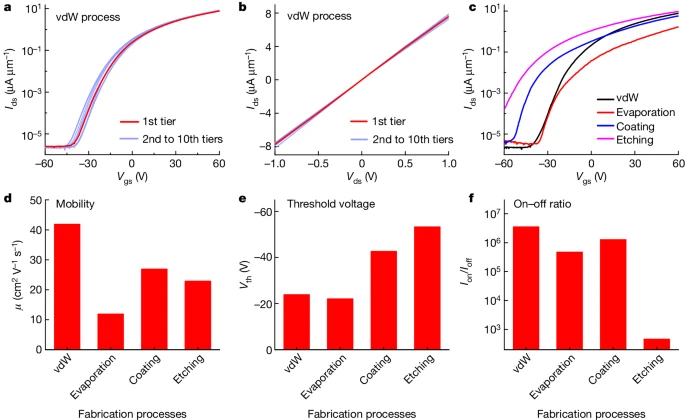

图2 使用不同制造工艺的二硫化钼晶体管的电学特性。

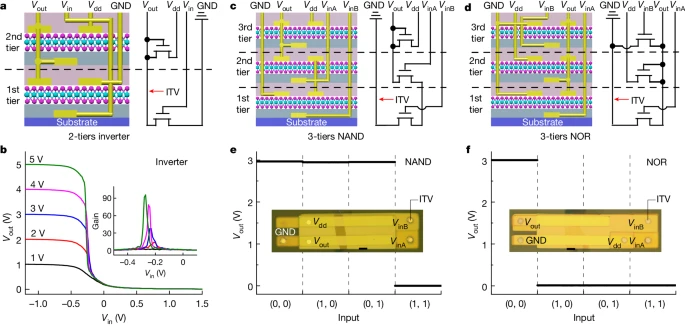

图3 由vdW M3D集成多个电路层的逻辑功能。

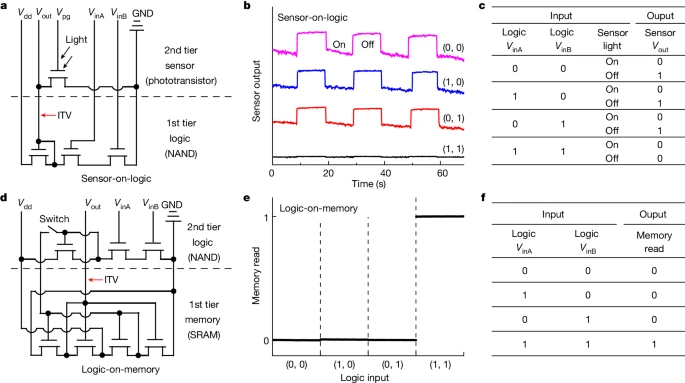

图4 异构M3D集成和垂直互联。

综上所述,研究者报告了一种可替代的低温无损伤M3D集成方法,使用二维半导体电路层层干层,从而克服了M3D集成的热预算限制,避免了较低层的性能下降。

使用这种技术,所有必要的器件组件都预制在牺牲晶圆上,然后通过一步vdW工艺在2D半导体上物理层压。使用这种技术,研究者已经成功地M3D集成了10层大规模2D晶体管,其中底部的2D晶体管在重复层压顶部电路层后不会受到影响。

总体而言,研究者的研究通过逐层vdW集成展示了一个晶圆级多层M3D集成系统,为制造具有更多堆叠电路层的M3D器件开辟了另一种方法。

【参考文献】

Lu, D., Chen, Y., Lu, Z. et al. Monolithic three-dimensional tier-by-tier integration via van der Waals lamination. Nature (2024). https://doi.org/10.1038/s41586-024-07406-z